Product Summary

The XC4020XLA-09PQ208C is a high-performance, high-capacity Field Programmable Gate Array which provides the benefits of custom CMOS VLSI, while avoiding the initial cost, long development cycle, and inherent risk of a conventional masked gate array. The result of fifteen years of FPGA design experience and feedback from thousands of customers, the XC4020XLA-09PQ208C combines architectural versatility, increased speed, abundant routing resources, and new, sophisticated software to achieve fully automated implementation of complex, high-density, high-performance designs.

Parametrics

XC4020XLA-09PQ208C characteristics: (1)INIT (High) setup time TIC: min=5 μs; (2)D0 - D7 setup time TDC: min=20 ns; (3)D0 - D7 hold time TCD: min=0 ns; (4)CCLK High time TCCH: min=45 ns; (5)CCLK Low time TCCL: min=45 ns; (6)CCLK Frequency FCC: max=10 MHz.

Features

XC4020XLA-09PQ208C features: (1)Footprint Compatible with XC4000XL FPGAs - Lower cost with improved performance and lower power; (2)Advanced Technology-5 layer metal, 0.25 μm CMOS process (XV) or 0.35 μm CMOS process (XLA); (3)Highest Performance-System erformance beyond 100 MHz; (4)High Capacity-Up to 500,000 system gates and 270,000 synchronous SRAM bits; (5)Low Power -3.3 V/2.5 V technology plus segmented routing architecture; (6)Safe and Easy to Use-Interfaces to any combination of 3.3 V and 5.0 V TTL compatible devices.

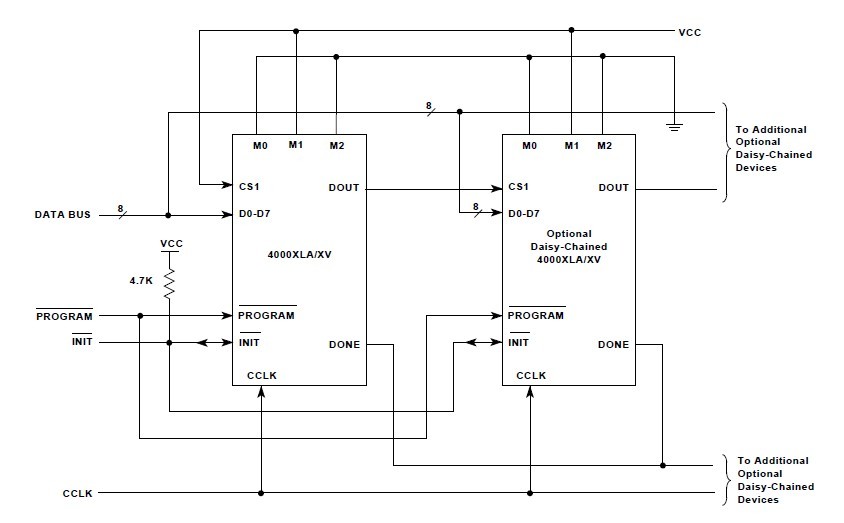

Diagrams

|

XC4000 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

XC4000A |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

XC4000E |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

XC4000H |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

XC4000X |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

XC4000XL |

Other |

|

Data Sheet |

Negotiable |

|

||||

(China (Mainland))

(China (Mainland))